12小时晶圆制程 集成电路前端工艺(FEO)详解与免费资源分享

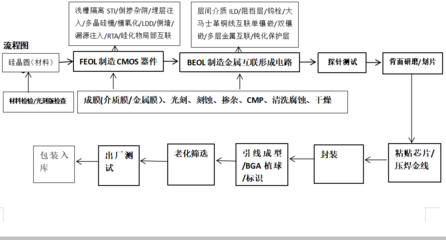

集成电路是现代电子设备的核心,其制造过程复杂而精密,通常分为前端工艺(FEO)和后端工艺(BEO)。前端工艺,即晶圆制造,是在硅片上形成晶体管、电阻、电容等元件的关键步骤。本文将聚焦于12小时晶圆制程中的前端工艺,并探讨集成电路芯片设计及服务,最后为您提供相关资源的免费获取途径。

一、前端工艺(FEO)的核心工序

前端工艺主要包括以下关键步骤,这些步骤在洁净室环境中进行,以确保芯片的高质量和可靠性:

- 晶圆制备:从高纯度硅锭切割出薄片(晶圆),并进行抛光处理,为后续工艺奠定基础。

- 氧化:在晶圆表面生长一层二氧化硅薄膜,用作绝缘层或掩模。

- 光刻:使用光刻胶和掩模版,通过曝光和显影,将电路图案转移到晶圆上。这是制程中最精细的环节,直接影响芯片性能。

- 刻蚀:去除未被光刻胶保护的部分,形成所需的物理结构。常用方法包括干法刻蚀和湿法刻蚀。

- 离子注入:将杂质离子注入晶圆特定区域,改变其电学特性,形成晶体管源极、漏极等。

- 薄膜沉积:通过化学气相沉积(CVD)或物理气相沉积(PVD)技术,在晶圆表面沉积金属或多晶硅层,用于互联。

- 化学机械抛光(CMP):平整化晶圆表面,确保多层结构的光滑度,便于后续加工。

这些工序通常循环进行,以构建多层电路结构。12小时制程指从晶圆入料到完成前端工艺的典型时间,实际时长因技术节点(如7纳米、5纳米)而异,需高度自动化和精准控制。

二、集成电路芯片设计及服务

前端工艺的实现离不开前端的芯片设计。芯片设计流程包括:

- 架构设计:定义芯片功能和性能指标。

- 逻辑设计:使用硬件描述语言(如Verilog)创建电路逻辑。

- 物理设计:将逻辑电路映射到物理布局,涉及布线、时序分析等。

- 验证与测试:通过仿真和原型测试确保设计正确性。

随着半导体行业的发展,设计服务也日益重要,包括IP核授权、设计外包、EDA工具支持等,帮助厂商缩短研发周期,降低成本。

三、免费资源下载与学习建议

对于初学者或从业者,了解前端工艺和设计知识至关重要。以下为免费资源推荐:

- 在线课程:Coursera、edX平台提供集成电路相关课程,如“VLSI设计”等。

- 开源工具:使用Qucs、Magic等开源EDA软件进行实践。

- 技术文档:半导体公司(如Intel、TSMC)常发布白皮书,介绍制程技术。

- 社区论坛:EETimes、Stack Exchange等社区有丰富讨论和资料分享。

第一部分免费下载提示:您可通过访问知名学术网站(如arXiv)或行业平台(如Semiconductor Engineering),搜索“FEO process guide”或“IC design basics”获取PDF资料。注意确保来源的合法性和安全性。

前端工艺是芯片制造的基石,结合精心的设计和专业服务,推动着半导体技术的不断进步。通过利用免费资源,您可以深入这一领域,为技术创新贡献力量。

如若转载,请注明出处:http://www.ghdbjdj.com/product/26.html

更新时间:2026-04-10 07:18:17