一文读懂集成电路产业版图设计过程

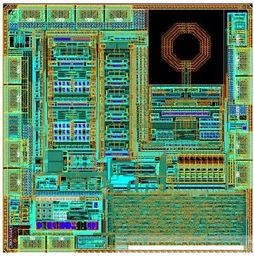

集成电路(IC)是现代电子设备的核心,其诞生过程犹如在微观世界构建一座精密城市。从最初的概念到最终投入生产,集成电路的版图设计是连接逻辑设计与物理实现的关键桥梁。本文将系统梳理集成电路芯片设计与服务中的版图设计全过程。

一、设计起点:逻辑设计与规格定义

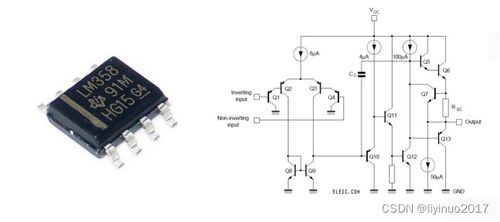

版图设计并非凭空开始,它基于完整的逻辑设计。设计团队根据芯片的功能需求(如处理器、存储器或专用ASIC),使用硬件描述语言(如Verilog或VHDL)完成寄存器传输级(RTL)设计,并借助电子设计自动化(EDA)工具进行逻辑综合,生成门级网表。需要明确工艺节点(如7纳米、14纳米)、性能、功耗和面积等关键规格,这些将直接影响版图的物理约束。

二、物理设计:版图实现的四大核心阶段

1. 布局规划(Floorplanning)

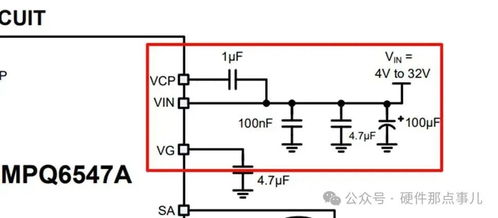

这是版图设计的宏观蓝图阶段。工程师需确定芯片的整体形状、尺寸,并规划主要功能模块(如CPU核、内存控制器、I/O接口)的位置。目标是优化布线资源、减少信号延迟,并确保电源网络均匀分布。合理的布局规划能显著提升芯片性能并降低后期调整成本。

2. 布局(Placement)

在布局规划框架下,将门级网表中的标准单元(如逻辑门、触发器)精确放置到芯片区域内。布局需平衡多个目标:最小化互连长度以降低延迟和功耗,避免布线拥堵,并满足时序要求。现代EDA工具通常采用自动布局算法,但工程师仍需手动优化关键路径。

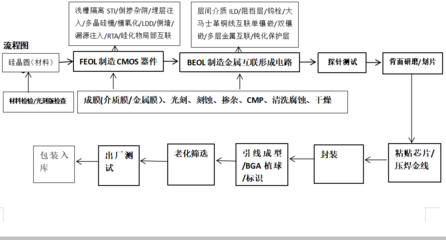

3. 布线(Routing)

布线是连接所有已放置单元的金属连线过程,如同为城市铺设道路。它分为全局布线和详细布线两步:全局布线规划连线大致路径,避免区域拥堵;详细布线则实际生成符合设计规则的金属层图形。布线必须严格遵守代工厂的工艺设计规则(DRC),确保可制造性。

4. 验证与优化

版图初步完成后,需经过严格验证:

- 设计规则检查(DRC):确保版图符合制造工艺的物理限制(如线宽、间距)。

- 电气规则检查(ERC):检测短路、开路等电气错误。

- 版图与原理图对照(LVS):验证版图实现的电路与原始网表一致。

- 时序与功耗分析:提取寄生参数进行仿真,优化关键路径以满足时序要求。

三、设计服务与产业协作

集成电路设计日益复杂,多数公司依赖专业的设计服务生态:

- EDA工具供应商(如Synopsys、Cadence):提供全流程软件平台,是版图设计的“工具箱”。

- 知识产权(IP)提供商:提供预设计的标准单元库、内存编译器及接口IP,加速版图构建。

- 晶圆代工厂(Foundry):提供工艺设计套件(PDK),包含设计规则、器件模型和标准单元库,是版图与制造衔接的基石。

- 设计服务公司:为无厂(Fabless)芯片公司提供从RTL到GDSII版图文件的端到端服务,尤其擅长先进工艺节点设计。

四、挑战与趋势

随着工艺进入纳米尺度,版图设计面临多重挑战:

- 物理效应凸显:信号完整性、功耗完整性和工艺变异影响加剧,需在版图中引入冗余设计、时钟树优化等对策。

- 设计成本攀升:先进节点的一次流片费用可达数千万美元,推动了对硅前验证和可制造性设计(DFM)的极致追求。

- 自动化与AI融合:机器学习技术正被用于预测布线拥堵、优化布局,提升设计效率。

###

集成电路版图设计是艺术与工程的结合——既需微观尺度的精确控制,又需宏观层面的系统思维。从逻辑设计到GDSII交付,每一步都凝聚着跨学科协作与技术创新。随着异构集成、Chiplet等新范式兴起,版图设计将持续演进,为算力时代铸造更强大的“硅基基石”。

如若转载,请注明出处:http://www.ghdbjdj.com/product/29.html

更新时间:2026-04-18 08:19:09